研究成果詳細

等価換算膜厚0.37nmのHigh-kゲート絶縁膜トランジスタの良好な動作を確認

要約

東京工業大学大学院総合理工学研究科の角嶋邦之助教,フロンティア研究センターの岩井洋教授らは,LSI微細化のネックとなっていたゲート絶縁膜の薄膜化に成功した.回路線幅16nm以降の次世代LSI実現の道を開く成果といえる.微細シリコンCMOSトランジスタの性能向上と低消費電力化のためにHigh-k(高誘電率)ゲート絶縁膜の更なる薄膜化が必須の技術である.しかしながら,ITRS(国際半導体ロードマップ)2007ではゲート絶縁膜の薄膜化は2012年に0.5nmの等価換算膜厚(EOT)に到達し,それ以降は薄膜化が進まないということになっており,その後のCMOS微細化による性能向上に関し大きな懸念となっていた.

研究の内容,背景,意義,今後の展開等

東京工業大学大学院総合理工学研究科の角嶋邦之助教,フロンティア研究センターの岩井洋教授らは,LSI微細化のネックとなっていたゲート絶縁膜の薄膜化に成功した.回路線幅16nm以降の次世代LSI実現の道を開く成果といえる.

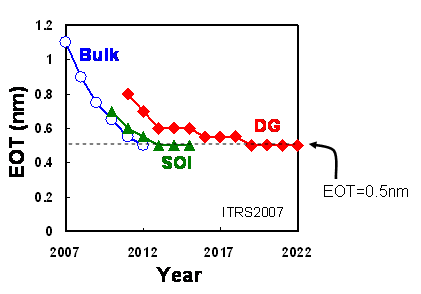

微細シリコンCMOSトランジスタの性能向上と低消費電力化のためにHigh-k(高誘電率)ゲート絶縁膜の更なる薄膜化が必須の技術である.しかしな がら,ITRS(国際半導体ロードマップ)2007ではゲート絶縁膜の薄膜化は2012年に0.5nmの等価換算膜厚(EOT)に到達し,それ以降は薄膜 化が進まないということになっており,その後のCMOS微細化による性能向上に関し大きな懸念となっていた.

本研究ではHigh-kゲート絶縁膜として酸化ランタン(La2O3)を用い,シリコン基板とHigh-kゲート絶縁膜の直接接合を実現することにより0.5nmの限界を打ち破って世界で始めてEOT=0.37nmのゲート絶縁膜を有するトランジスタの作製に成功し,その良好な動作を確認した.

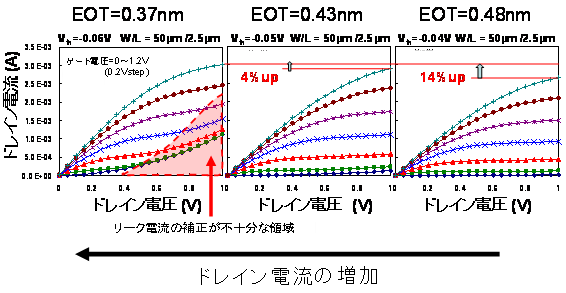

性能に関してはEOT=0.5nmから0.37nmに薄膜化することによって14%のドレイン電流の増加を確認した.この値は反転層容量も含めたゲートの容量比に対応する.

本成果は本日11月5日から3日間の予定で東京で開催される誘電体薄膜国際会議International Workshop on Dielectric Thin Film 2008 (IWDTF2008)で発表された.

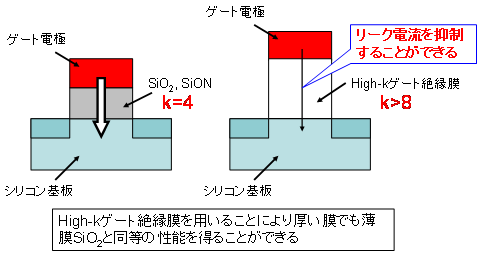

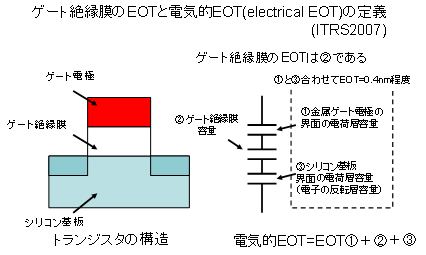

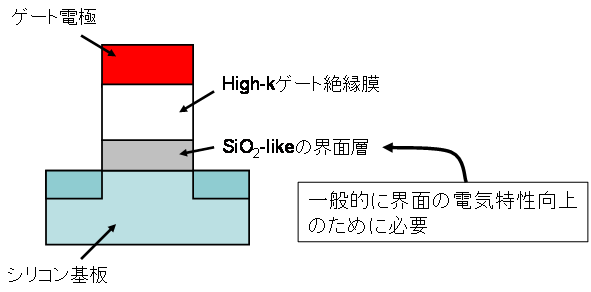

大規模集積回路(LSI)を構成するシリコン相補型金属酸化膜半導体(CMOS)トランジスタの性能向上と低消費電力化はスケーリング則に基づくトラン ジスタの微細化によって達成されてきた.この微細化のボトルネックがゲート絶縁膜の薄膜化である.従来はシリコン酸化膜(SiO2)やシリコン酸窒化膜(SiON)などの薄膜がゲート絶縁膜として用いられてきたが,数年前からその膜厚が1.2nmに達し,直接トンネル現象によるゲートリーク電流の増加がデバイスの仕様に耐えられないほどになってきた.この解決策として世界各国でSiO2やSiONを置き換えるhigh-k材料としてハフニウム酸化膜(HfO2)系のゲート絶縁膜が開発され,Intelなどでは昨年から実際の製品に用いられようになってきている.High-kゲート絶縁膜では誘電率がSiO2や SiONなどに比べて高いので,その分ゲート絶縁膜の物理的膜厚を増加させて直接トンネルリーク電流を抑制させ,なお且つ薄膜ゲート絶縁膜と同じ高性能な トランジスタ特性を得ることができる(図1).また,High-kゲート絶縁膜の薄膜化により更なる高性能化の実現が可能である.High-kゲート絶縁 膜の膜厚は,SiO2に換算した電気容量的に等価な膜厚:EOT(Equivalent oxide thickness)で表わし,薄膜化の指標とする(図2).

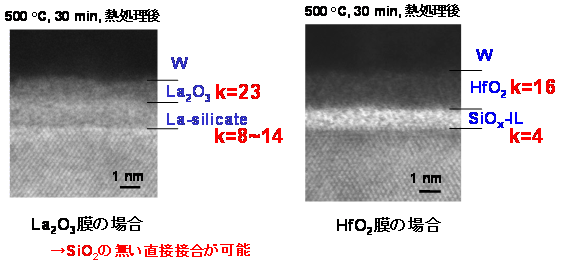

ところで,High-kゲート絶縁膜とシリコン基板との電気的特性は一般的には極めて悪い.これを回避するために,IntelなどはHigh-kゲート絶縁膜とシリコン基板の界面にはシリコン酸化膜を主成分とするSiO2-like の界面層を用いてHigh-k材料とシリコン基板との直接接合を避けている(図3).(参考文献:Jeffrey HicksらIntel Technology Journal? Volume 12? Issue 02? Published June 17? 2008).しかしながら,この界面層(物理膜厚1nm程度)はSiO2-likeであるため比誘電率は当然の事ながら低いことが予想され,この上にHfO2ベースのHigh-k絶縁膜が存在してもゲート絶縁膜としてのEOTを0.5nm以下にすることは不可能であると思われてきた.実際,HfO2ベースのHigh-kでは,SiO2-like の界面層を比誘電率が高めのHfシリケートに変えても今までトランジスタ動作が確認された最小のEOTは0.49nmであり(M. Takahashi他IEDM2007 pp.523の論文),0.5nmあたりに薄膜化の限界があるという認識に変わりはなかった.

今回東京工業大学の角嶋助教・岩井教授・Ahmet助教のグループはHigh-kゲート絶縁膜として酸化ランタン膜(La2O3) を用いることによりシリコン基板との直接接合を実現し,世界で初めてEOT=0.37nmのMOS電界効果トランジスタ(MOSFET)の良好な動作を実 験的に確認した.性能に関してはEOT=0.5nmから0.37nmに薄膜化することによって14%のドレイン電流の増加を確認した.この値は反転層容量 も含めたゲートの容量比に対応する.

ITRS2007でEOTが0.5nmに到達することが記述されている2012年は「22nmロジックCMOS技術」に対応する年と想定される.この後 ロジックCMOS技術は16nm,11nm,8nmと世代が続くことが予測されているが,ゲート絶縁膜の薄膜化はEOT=0.5nmで打ち止めとなってお りこのままでは短チャネル効果の抑制やドレイン電流の性能向上に大きな支障が出るのではないかと思われてきた(図4).今回,EOT=0.37nmのゲー ト絶縁膜の作製が可能なことが実験的に確認され,尚且つそれを用いたMOSFETの電流増加がゲート絶縁膜の薄膜化から期待された通りの値が得られたこと はCMOSの微細化を16nm以降に推し進める上で大変に大きな意義を有する.また,短チャネル効果の抑制という観点からプレーナ型のいわゆるバルクトラ ンジスタはITRS2007では2012年の22nmロジックCMOSが最後とされ,その後はSOIやダブルゲート(DG)が用いられるとされている が,16nmまでプレーナ型のバルクトランジスタが用いられる可能性もでてきた.

今回トランジスタ動作を確認したデバイスは,ゲート絶縁膜としてLa2O3膜を採用した.La2O3膜は誘電率が高く(比誘電率24程度)バンドギャップが広い(5.5eV程度)ため,リーク電流の抑制に効果的である.La2O3は酸素の供給によりシリコンと界面反応を起こし,Laシリケート層を形成し,このLaシリケート層の比誘電率は反応するシリコン量による濃度で8~14となる.一方でHfO2はシリコンとの界面反応によりSiO2を形成する(図5).そのため,小さいEOTの達成に有利な直接接合界面の実現にLa2O3は有効な材料である.La2O3膜の堆積は超高真空中における酸化ランタン焼結体の電子線蒸着で行った.この装置は内部に可動シャッターを装備しており,複数の基板に異なる膜厚の酸化ランタンを一回の実験で堆積することが可能である.メタルゲート電極はタングステンを選択し,La2O3膜上に超高真空を維持したまま外気に触れることなく形成することで,La2O3膜の強い吸湿性による劣化を防ぐことが可能である.

本研究ではトランジスタの低温での作製を可能とするゲートラストプロセスを採用したデバイスの作製を行ったため,La2O3膜とシリコン基板の反応によるLaシリケート膜の形成を極力抑制し,低いEOTの実現が可能となった.作製したトランジスタは2.5 μmのゲート長,50μmのゲート幅をもつnチャネルのトランジスタである.

電気測定の結果,作製したデバイスは正常にトランジスタ動作をしていることが確認でき,さらに薄膜化に伴うドレイン電流の増加を確認することに成功した (図6).移動度が一定であると仮定した場合のドレイン電流の増加分からEOTを算出すると,ITRSでは2012年頃に実現すべき0.5nmのEOTよ りも小さい0.37nmであることがわかった.以上の結果より,0.5nm以下のEOTでも電流増加が実現でき,ゲート絶縁膜の薄膜化スケーリングによる 性能向上がまだ可能であることを示すことに成功した.今後,この技術が製品に用いられるようになる為には,更なるゲートリーク電流の低減や移動度の向上, 高温耐熱性などを実現する研究が必要となるが,本研究が0.5nm以下のゲート絶縁膜への道を拓いた意義は大きい.

本研究はNEDO委託研究「次世代半導体材料・プロセス基盤(MIRAI)プロジェクトにおける先導研究/次世代high-k・メタルゲートスタック技術に関する先導研究」の支援によって行われた.

本成果は本日11月5日から3日間の予定で東京で開催される誘電体薄膜国際会議International Workshop on Dielectric Thin Film 2008 (IWDTF2008)で発表された.

|

|

|

図3 界面層挿入の必要性 界面特性の向上のためにHigh-kゲート絶縁膜とシリコン基板の間にSiO2-likeの界面層が必要である. |

図4 EOT<0.5nmのトランジスタの電気特性評価 ITRS2007では2012年にEOT=0.5nmの達成を要求しているがその後は薄膜化は打ち止めになっている.またSOIやダブルゲート(DG)でもEOTは0.5nmまでである. |

| 本件に関するお問い合せ先 |

|

|---|---|

| TEL | |

| FAX | |

| URL |

*6年以上前の研究成果は検索してください