研究成果詳細

ミリ波帯無線通信の実用化にめど

要約

東京工業大学大学院理工学研究科の松澤昭教授、岡田健一准教授らの研究グループは雑音を従来の100 分の1以下に低減したミリ波帯局部発振器(用語1)を開発した。20GHz 帯の発振器と60GHz 帯の注入同期型直交局部発振器を組み合わせることにより、世界最高の低位相雑音性能を達成した。無線通信の周波数帯ひっ迫を解消する技術として60GHz帯(ミリ波帯)の利用が注目されているが、ミリ波帯ではコイルやコンデンサの損失が大きくなり、位相雑音(用語2)特性が劣化するのがネックだった。今回はこれを解決したもので、ミリ波無線通信の実用化につながる成果だ。

研究の内容,背景,意義,今後の展開等

【概要】

東京工業大学大学院理工学研究科の松澤昭教授、岡田健一准教授らの研究グループは雑音を従来の100 分の1以下に低減したミリ波帯局部発振器(用語1)を開発した。20GHz 帯の発振器と60GHz 帯の注入同期型直交局部発振器を組み合わせることにより、世界最高の低位相雑音性能を達成した。

無線通信の周波数帯ひっ迫を解消する技術として60GHz帯(ミリ波帯)の利用が注目されているが、ミリ波帯ではコイルやコンデンサの損失が大きくなり、位相雑音(用語2)特性が劣化するのがネックだった。今回はこれを解決したもので、ミリ波無線通信の実用化につながる成果だ。

発振器は65 ナノメートル(nm) のシリコンCMOS プロセスを利用して試作した。58.0GHz から63.6GHz の周波数範囲で4相正弦波出力(用語3)が可能である。この発振器により、10Gbps(毎秒100 億ビット)以上の超高速ミリ波帯無線通信の実現が期待される。

この成果は8日から北京で開かれる「アジア固体回路国際会議」で10 日に発表する。

●研究の背景と本成果の意義

現在、携帯電話や無線LAN などの公衆向け無線通信機器には、6GHz 以下の周波数が利用されている。6GHz 以下の周波数帯は既に様々な無線通信に利用されており、それぞれの無線通信規格で利用できる周波数帯域はごく限られたものである。実用化されている中で一 番高速な無線LAN 規格であるIEEE802.11n でも40MHz の周波数帯域しか利用できず、伝送速度も高々300Mbps 程度である。無線伝送速度は周波数帯域で制限されるため、このような逼迫した6GHz 以下の周波数を利用する限り、今以上の大幅な速度向上は期待できない。

そのような中、近年注目を集めているのは60GHz 帯を用いるミリ波無線通信である。60GHz では最大で9GHz 近い帯域の利用が可能であり、大幅な通信速度の向上が期待できる(参考図)。60GHz 帯には2.16GHz 帯域が4 チャネル確保されており、通常用いられるQPSK 変調(用語4)では1 チャネルあたり3.5Gbps、より高度な16QAM 変調(用語5)では1チャネルあたり7Gbps の無線伝送が可能である。4 チャネル同時に利用すれば28Gbps の無線伝送が可能である。このようにミリ波帯で16QAM 変調が可能になれば、大幅な無線通信速度の向上が実現できる。

ミリ波無線通信の実用化に向けて、現在盛んに研究開発が行われているが、位相雑音(用語2)を 改善できないことが最大の課題となっている。本開発回路方式では、60GHz 帯の発振器と20GHz 帯の発振器を組み合わせることにより、大幅な位相雑音特性の改善を達成した。本開発回路を用いれば、16QAM 変調による10GHz 超の伝送速度の実現が可能である。

●発表予定

この成果は,11月8日~10日に中国の北京で開催される「2010 IEEE Asian Solid-StateCircuits Conference (A-SSCC 2010):2010年IEEE アジア固体回路国際会議」のセッション「Session 7 - High-precision PLLs and Low-power Circuits for Communication」で発表する。講演タイトルは「A 58-63.6GHz Quadrature PLL Frequency Synthesizer in 65nm CMOS (65nmCMOSプロセスによる58GHzから63.6GHzの出力可能な直交局部発振器)」である。11月10日の10時45分から発表を行う。

なお、本研究は総務省委託研究「電波資源拡大のための研究開発」の一環として実施された。

● 技術内容

開発した回路では,58.0GHz から63.6GHz の周波数範囲において、4相正弦波出力(用語3)が可能であり、位相雑音特性(用語2)に おいて世界最高性能を達成した。従来、4相正弦波出力が可能な発振器の位相雑音は1MHz 離調で-75dBc/Hz であったのに対し、本開発回路では-96dBc/Hz となり、従来の1/126 以下(21dB 改善)に雑音を低下させること成功した。高速な無線通信が可能な16QAM 変調(用語5)のためには、-90dBc/Hz 以下の位相雑音特性が必要であったが、本開発回路はそれを上回る性能を達成した。

16QAM 変調は高速な無線伝送が可能である一方、高い回路性能を要求するため、従来ミリ波帯では実現が困難とされてきた。ミリ波無線通信で16QAM 変調が困難な理由として、ミリ波帯ではコイルやコンデンサの損失が大きく、必要な位相雑音特性が得られないということが挙げられる。また、小型・低消費電 力なダイレクトコンバージョン型の無線機実現のためには、4相正弦波出力が必要であり、これまで報告のあったものでは、位相雑音性能が低く、QPSK 変調ですら困難な性能であった。

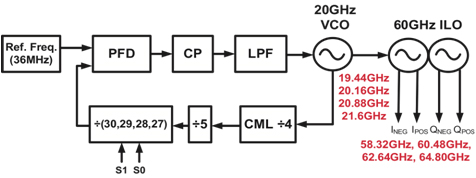

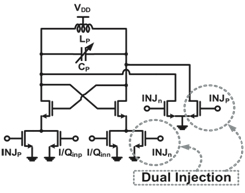

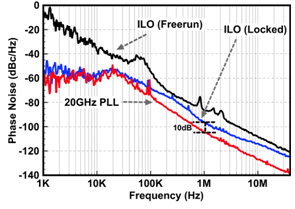

本開発回路方式では、60GHz 帯の発振器と20GHz 帯の発振器を組み合わせることにより、大幅な位相雑音特性の改善を可能とした。図1が開発した回路のブロック図である20GHz帯における発振器 (PLL: Phase-Locked Loops)と、60GHz 帯における注入同期型直交発振器(ILO: Injection-Locked Oscillator)により構成される。図2が注入同期型直交発振器(ILO)である。20GHz 帯PLL で生成した低位相雑音な正弦波信号を、60GHz 帯注入同期型直交発振器(ILO)に入力することにより、60GHz 帯での位相雑音特性を大幅に改善し、なおかつ、4相正弦波が出力可能である。図3が実測した位相雑音特性であり、単体のILO にくらべ60dB以上の位相雑音改善効果が得られた。

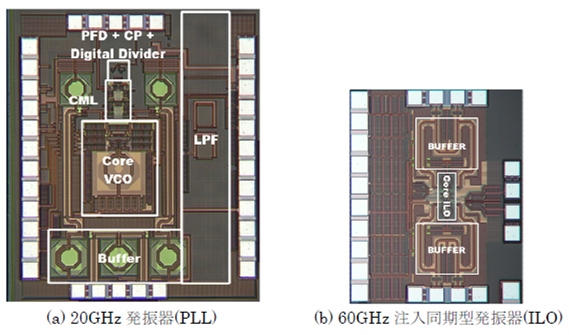

図4が実際に作成したチップの写真である。65nm CMOS プロセスにより試作した。従来報告のあったミリ波帯発振器との性能比較を表1に示す。これまでにミリ波帯で4相発振器として報告があったのは1例のみであ り、本開発回路はその位相雑音特性を21dB(1/126)以上低下させること成功した無二の回路である。

本開発回路を用いれば、ミリ波帯での16QAM 変調が実現可能であり、これまでにない10Gbps 以上の高速な無線伝送速度を利用可能となる。

【用語説明】

用語1:局部発振器

局部発振器は,無線通信に必要な搬送波信号を生成するための回路である。通常、基準となる水晶発振器と、位相同期ループ(PLL:Phase-Locked Loops)により構成される。無線機の性能を左右する最重要構成要素であり、通信品質の改善のため、低位相雑音(用語2)であることが必要とされる。直交局部発振器は、4相正弦波(用語3)の出力が可能な局部発振器である。

用語2:位相雑音

発振器の重要な特性の一つ。必要な周波数の信号に対し,どれだけ不要な周波数のスペクトルを持つかを表す。

用語3:4相正弦波

通 常用いられる差動型発振器には,出力が2端子あり,それぞれ0 度と180 度の位相を持つ正弦波が出力される。一方で,無線通信機には4相の正弦波が必要であり,0度,90 度,180 度,270 度に位相のずれた4 つの正弦波が必要である。2つの差動型発振器を組み合わせる方法や,原発振を2倍の周波数とし,周波数分周器を用いて4位相を発生させる方法などが用いら れる。

用語4:QPSK 変調

位相偏移変調の一種。一回の変調で2bit の情報伝送が可能である。

用語5:16QAM 変調

直交位相振幅変調の一種。位相と振幅の両方に変調をかけることにより、一回の変調で4bit の情報伝送が可能である。

【本研究の講演日時】

2010年11月10日(水) 10時45分 (現地時間) 口頭発表

【論文タイトル】

A 58-63.6GHz Quadrature PLL Frequency Synthesizer in 65nm CMOS

(65nm CMOSプロセスによる58GHzから63.6GHzの出力可能な直交局部発振器)

【著者】

Ahmed Musa (博士課程学生 [登壇者])? Rui Murakami (村上 塁:修士課程学生)?

Takahiro Sato (佐藤 高洋:修士課程学生)? Win Chaivipas (博士課程卒業生)?

Kenichi Okada (岡田健一:准教授)? Akira Matsuzawa (松澤 昭:教授)

【会議公開情報】

http://www.a-sscc.org/

Session 7-2

A 58-63.6GHz Quadrature PLL Frequency Synthesizer in 65nm CMOS

Abstract

This paper proposes a 60GHz quadrature PLL frequency synthesizer that has a tuning range capable of covering the whole band specified by the IEEE802.15.3c with exceptional phase noise. The synthesizer is constructed using a 20GHz PLL that is coupled with a frequency tripler to generate the 60GHz signal. The 20GHz PLL generates a signal with a phase noise as low as -106dBc/Hz using tail feedback to improve the phase noise. The proposed 60GHz ILO uses a combination of parallel and tail injection to enhance the locking range? which is called dual-injection ILO. Both the 20GHz PLL and the ILO were fabricated using a 65nm CMOS process and measurement results show a phase noise of -96dBc/Hz at 60GHz while consuming 77.5mW from a 1.2V supply. This phase noise is 21dB(126 times) better then conventional PLLs.

|  |  |

| 図1: 提案回路構成 (20GHz 発振器(PLL)と60GHz 注入同期型発振器(ILO)を組み合わせることで実現) | 図2:提案型60GHz注入同期型発振器(ILO) | 図3:位相雑音特性 |

|

| 図4:チップ写真 (65nm CMOS プロセスにより製造) |

| 本研究 | [1] | [2] | [3] | [4] | |

|---|---|---|---|---|---|

| 周波数範囲 [GHz] | 58~64 | 57~66 | 64~66 | 51~53 | 58~60 |

| 消費電力 [mW] | 77.5 | 78 | 72 | 87 | 80 |

| 位相雑音(1MHz 離調) [dBc/Hz] | -96 | -75 | -84 | -85 | -85 |

| 出力相数 | 4相 | 4相 | 2相 | 2相 | 2相 |

表1:従来報告のあったミリ波帯発振器(PLL)との性能比較

(従来のミリ波帯発振器と比較し,21dB(126 倍)以上の低位相雑音化を実現)

[1] K. Scheir, G. Vandersteen, Y. Rolain, and P. Wambacq, "A 57-to-66GHz Quadrature PLL in 45nm Digital CMOS," IEEE International Solid-State Circuits Conference (ISSCC), pp. 494-495, Feb. 2009.

[2] K.-H. Tsai, J.-H. Wu, and S.-I. Liu, "A Digitally Calibrated 64.3-66.2GHz Phase-Locked Loop," IEEE Radio Frequency IC Symposium (RFIC), pp. 307-310, June 2008.

[3] C. Lee, L.-C. Cho, J.-H. Wu, and S.-I. Liu, "A 50.8-53GHz Clock Generator Using a Harmonic-Locked PD in 0.13um CMOS," IEEE Transactions on Circuits and Systems II, vol. 55, no. 5, pp. 404-408, May 2008.

[4] C. Lee and S. L. Liu, "A 58-to-60.4GHz Frequency Synthesizer in 90nm CMOS," IEEE International Solid-State Circuits Conference (ISSCC), pp. 196-197, Feb. 2007.

| 本件に関するお問い合せ先 |

|

|---|---|

| TEL | |

| FAX | |

| URL |

*6年以上前の研究成果は検索してください