研究成果詳細

次世代半導体の信号処理を高速化するオンチップ通信技術

要約

本学統合研究院の益一哉教授と岡田健一准教授,伊藤浩之助教らの研究グループは,次世代シリコンCMOS半導体の信号処理を大幅に高速化するオンチップ通信技術を開発し,実際に回路チップを試作して性能を確認した.本成果は,2007年6月に京都で開催された半導体回路技術の国際会議「2007 Symposia on VLSI Circuits」において「A 8-Gbps Low-Latency Multi-Drop On-Chip Transmission Line Interconnect with 1.2-mW Two-Way Transceivers (1.2mW Two-Way Transceiversを有する8Gbps低レイテンシ・マルチドロップオンチップ伝送線路配線)」の題目で発表された.

研究の内容,背景,意義,今後の展開等

本学統合研究院の益一哉教授と岡田健一准教授,伊藤浩之助教らの研究グループは,次世代シリコンCMOS半導体の信号処理を大幅に高速化するオンチップ通信技術を開発し,実際に回路チップを試作して性能を確認した.

本成果は,2007年6月に京都で開催された半導体回路技術の国際会議「2007 Symposia on VLSI Circuits」において「A 8-Gbps Low-Latency Multi-Drop On-Chip Transmission Line Interconnect with 1.2-mW Two-Way Transceivers (1.2mW Two-Way Transceiversを有する8Gbps低レイテンシ・マルチドロップオンチップ伝送線路配線)」の題目で発表された.

大規模な高速CMOS半導体チップは、CPUやメモリ,DSP,エンコーダ,デコーダなどの回路ブロック(コア)で構成されている.これらのコア間では、ひんぱんに電気信号をやり取りする.このため,コア間の通信路には高い伝送速度が要求される.

電気信号の伝送速度を上げていくと,電気信号の伝送を電流ではなく,電磁波として取り扱わなければならない領域に達する.これは伝送速度(伝送周波数)と 伝送距離によって決まり,伝送距離が長い場合は伝送速度が比較的低くても,電磁波として扱う領域に達する.例えば外形寸法が10cm角を超えるプリント基 板では,伝送周波数が数百MHzになると、電気信号を電磁波として取り扱うようになっていた.

これに対して半導体チップは伝送距離が 10mm~20mm程度と短いので,これまでは電磁波として扱わずに済んでいた.しかし最近では通信路(配線)当たりの伝送速度が1Gビット/秒を超える ようになり,通信路(配線)を伝送線路(信号を電磁波として伝送するための導波路)として扱う必要性が増してきた.にもかかわらず,シリコン半導体チップ で伝送線路を構築する研究はこれまで,あまりなかった.

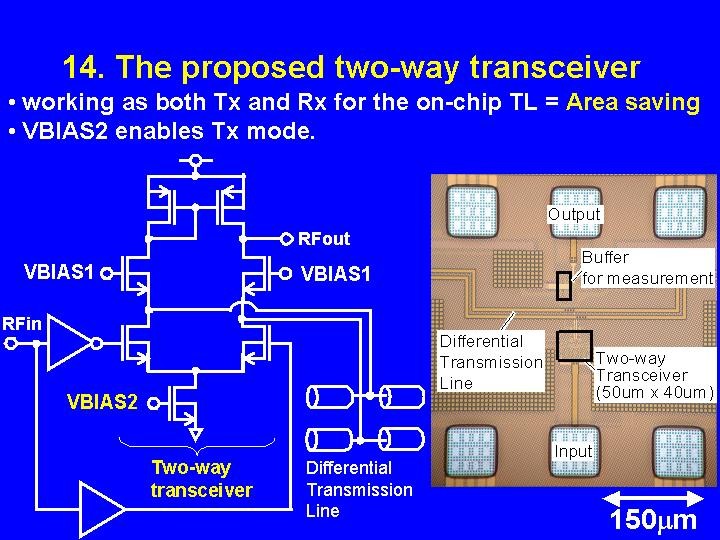

そこで益教授らのグループは,シリコン半導体チップ上の伝送信号を電磁波として 扱う送受信技術を開発した.伝送線路には「コプレーナ線路」と呼ばれる代表的な線路を選び,差動信号で伝送することにした.高速性と低い消費電力を両立さ せるためである.送受信回路(トランシーバ回路)には,送信と受信を切り換えられる回路を考案した.送信時の出力インピーダンスは伝送線路の特性インピー ダンスとほぼ同じなので,信号を円滑に出力できる.受信時の入力インピーダンスは高く,複数の送受信回路を通信路に接続した場合でも信号波形の歪みを抑え られる.

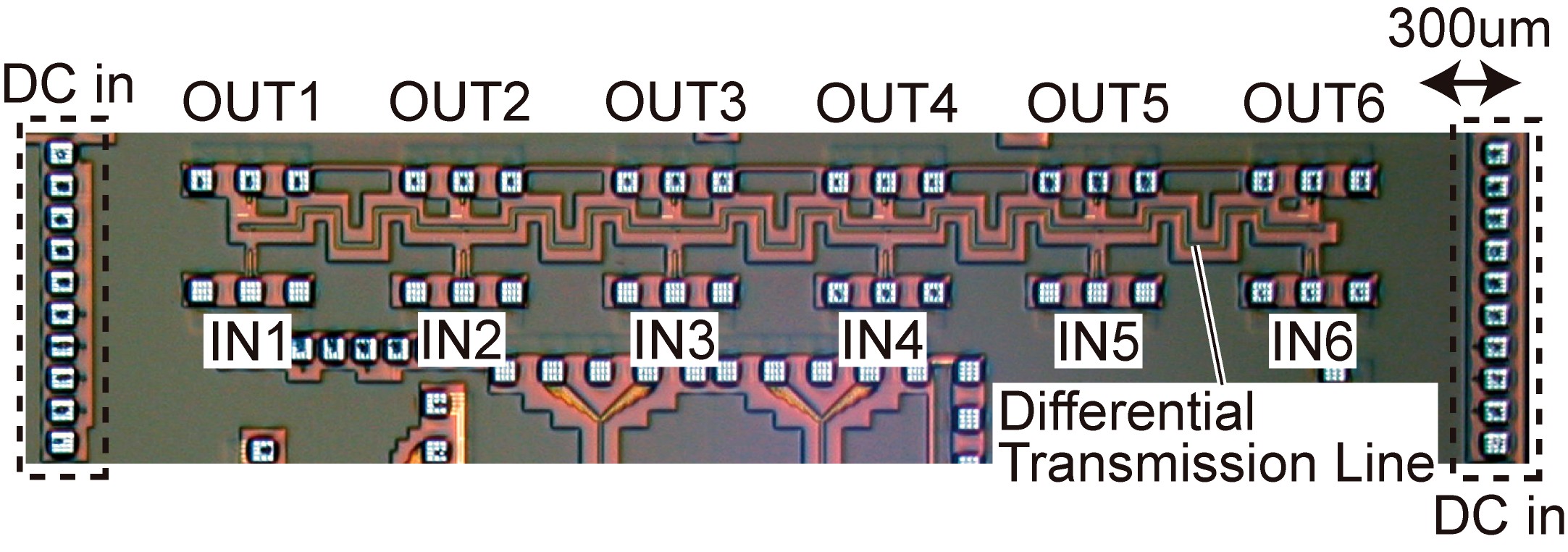

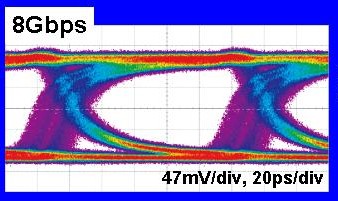

今回は90nmと非常に微細なCMOSプロセス技術を駆使し,長さ5mmの伝送線路と6個の送受信回路を搭載したテストチップを試作し てみせた.そして実際に8Gビット/秒と高い速度でデータ信号を伝送した.入出力間の遅延時間は115ps/5mmである.1ビットデータの伝送に必要な 消費電力は0.87pJだった.このことから,従来の送受信技術に比べて3分の1程度の回路面積と消費電力で信号を伝送できることが示された.

今後,回路や伝送線路などを改良していけば,10Gビット/秒を超える伝送は十分に可能であると益教授らは予測している.

なお本研究は,新エネルギー・産業技術総合開発機構の「次世代半導体材料・プロセス基盤(MIRAI)プロジェクトにおける先導研究」の受託研究テーマ「新探求伝送線路配線技術に関する研究」に採用されている.

|

|

|

|

図1 試作したチップの写真 6個の送受信回路(トランシーバ)と差動伝送線路で構成した |

図2 開発した送受信回路(トランシーバ) 1個の回路で送信と受信を兼ねる.左は回路図.右は試作チップの拡大写真 |

図3 試作チップで8Gビット/秒のデータ信号を伝送したときの信号波形 |

| 本件に関するお問い合せ先 |

|

|---|---|

| TEL | |

| FAX | |

| URL | http://www.masu-lab.com/ |

*6年以上前の研究成果は検索してください